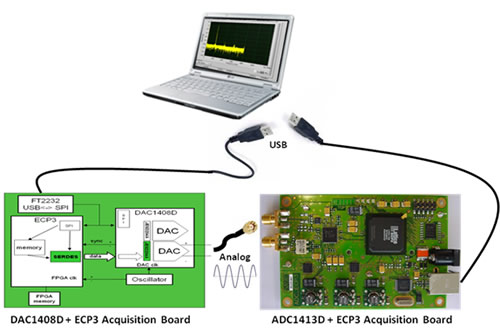

5月27日,恩智浦半导体(NXP Semiconductors)宣布,CGV™高速数据转换器系列新增两款低成本、低功耗演示板,新产品采用了莱迪思半导体公司(纳斯达克上市公司:LSCC;公司总部位于俄勒冈州希尔巴罗市)生产的LatticeECP3™器件。新演示板旨在证明恩智浦CGV转换器与莱迪思ECP3 FPGA系列器件的互通性。演示板1集成了恩智浦ADC1413D和莱迪思ECP3器件;演示板2集成了恩智浦DAC1408D和莱迪思ECP3器件。恩智浦将在2010年5月25日至27日加州阿纳海姆市举行的IEEE微波理论与技术协会(MTT-S)/ 国际微波年会(IMS)上展示DC1413D演示板,展位号3324。

恩智浦CGV高速数据转换器针对JEDEC JESD204A标准串行接口进行优化设计,不仅大幅减少了数据转换器与VLSI逻辑器件之间的互联信号数量,还能通过多数据转换器通道的同步绑定解决复杂的客户设计问题。

莱迪思半导体公司欧洲市场部经理Ron Warner表示:“我们非常高兴能与恩智浦合作开发新型演示板,开展JESD204A标准接口互通性测试工作。针对JESD204A开发应用,莱迪思公司为系统设计人员提供了成本最低、功耗最小的ECP3 FPGA系列产品。”

恩智浦半导体高速转换器事业部高级总监兼产品线经理Maury Wood表示:“我们非常高兴通过这两块演示板来证明恩智浦新型CGV转换器与莱迪思ECP3 FPGA器件的互连互通。无论是从事基站还是高速仪器仪表的设计工程师,都可以在此参考设计的基础上,针对实际要求开展设计工作。”

新演示板采用USB供电方式,利用单台笔记本电脑和两个备用USB端口,运行LabView或其他信号分析软件即可实现配合使用的目的(DAC板的信号输出作为ADC板的信号输入)。

CGV™ (Convertisseur Grande Vitesse)表明恩智浦兼容JEDEC JESD204A接口标准,支持超集实施方案,能够显著改善转换器速率(最高达4.0 Gbps,标准速率为3.125 Gbps,增幅28%)和转换器传输距离(最大100 cm,标准范围为20 cm,增幅达400%)。增强的CGV功能还包括 DAC1408D系列D/A转换器的多器件同步(MDS)。恩智浦实施这一可选功能的目的,在于为LTE MIMO基站及其他高级多通道应用创造条件。恩智浦的MDS实施方案最多可对16个DAC数据流进行同步采样,同时保持相位一致。

LatticeECP3系列是莱迪思半导体公司推出的第三代高性价比FPGA,是业界成本最低、功耗最小,支持SERDES接口标准的FPGA器件。LatticeECP3 FPGA系列器件支持多协议3.2G SERDES和XAUI抖动标准、DDR3存储器接口、功能强大的DSP技术和高密度的片上存储器(高达149K LUT),所有器件的功耗和价格只有支持SERDES功能的同类FPGA的一半。